ISSN: 2455-8761

www.ijrerd.com || Volume 02 – Issue 06 || June 2017 || PP. 111-115

# Design of Fully Reused DSRC Encoders using SOLS Technique

# Sreelakshmi K P<sup>1</sup>, Baby Vineetha<sup>2</sup>

<sup>1</sup> Mtech Student, MET'S School of Engineering, Mala, Thrissur, Kerala <sup>2</sup> Professor, MET'S School of Engineering, Mala, Thrissur, Kerala

**Abstract:** In the communication system the secure data transmission is very important. There are numbers of encoding techniques are used for the communication of data in DSRC. Several types of applications such as FM0, miller and Manchester encoding are used for the communication which provides the security to the data. The dedicated short-range communication (DSRC) system is the evolving technique used in the field of intelligent transport system (ITS) and Electronic Toll Collection (ETC). For obtaining DC balance, signal reliability, and to avoid noise interference DSRC adopts FMO, Manchester and Miller encoding. In this paper, Similarity Oriented Logic Simplification (SOLS) provides 100% Hardware Utilization Rate.

**Keywords:** FMO, Manchester, DSRC(Dedicated Short Range Communication), SOLS(Similarity Oriented Logic Simplification), ITS(Intelligent Transportation System), ETC(Electronic Toll Collection)

#### I. INTRODUCTION

Encoding technique is used in the communication system to convert the information of data into the suitable form of transmission. Encoding techniques are used for the purpose of security. There are different types of encoding techniques are used for the serial communication application. Several types of applications such as FM0, Manchester encoding, Miller encoding, NRZ, FM1, RZ, etc. are used for encoding of data in DSRC. The dedicated short-range communication (DSRC) is short range to medium range communication which can be communicated one or both ways in vehicle to vehicle (V2V) or vehicle to roadside (V2R) communications system. In vehicle -to- vehicle the DSRC equipment send and receives messages from one vehicle to other vehicle within the range. These messages include road safety instructions, traffic intimations; inter car distance, intersection warnings and collision alarms. The vehicle to roadside DSRC systems is mainly used for intelligent transport systems such as electronic toll collection, parking payments and gas refueling is used for encoding the data.

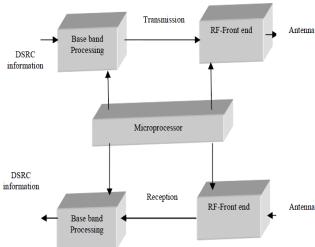

Figure 1: DSRC Transceiver

The architecture system of DSRC transceiver is as shown in Fig.1.The upper parts are dedicated for transmission and bottom parts are dedicated for receiving the information. The transceiver is classified into three modules: baseband processing, microprocessor, and RF front-end. The instructions of microprocessor interpret to schedule the tasks of baseband processing and RF front-end from media access control. The baseband processing is dependable for the error correction, modulation, and encoding and clock synchronization. The RF frontend transmits and receives the wireless signal through the antenna.

ISSN: 2455-8761

www.ijrerd.com || Volume 02 – Issue 06 || June 2017 || PP. 111-115

## II. LITERATURE REVIEW

In [1], author proposed fully reused VLSI (Very Large Scale Integration) architecture by using SOLS technique for both the FM0 and Manchester encoding. The SOLS technique eliminates the limitations of hardware utilization by using two core techniques- (1) Area compact retiming and (2) Balance logic-operation sharing techniques. The Area compact retiming is used to reduce the hardware problem like number of transistor and the balance logic operation sharing the help identical logic components can be efficiently combines with the FM0 and Manchester encoding. In this paper the proposed method works on parameters like low power consumption, high operating frequency etc. This paper develops a fully reused VLSI architecture and also exhibits a competitive performance compared with the existing works. In [2]and [5], it is shown that an unbalance computation time results in the glitch at the input of MUX that causes the logic fault on coding. This paper overcomes the problem of glitches by using XNOR with the inverter by replacing the XOR and this becomes the input of the MUX.

This is done to balance the computational time. The adoption of FM0 or Manchester code depends on Mode and CLR signal. In this design both modes are separately allocated to system controller. Whether FM0 or Manchester code is adopted, all the logic component of the proposed VLSI architecture is utilized and provides better results. The work in [3] presents a review on Manchester, Miller and FM0 encoding techniques. This paper presents the circuit design strategies of Manchester, Miller and FM0 using a finite state machine. A comparative study of all these techniques is also presented in this work. [4] proposes a new Manchester code generator which behaves as an edge-triggered D flip-flop, except that the output is inverted on the clock falling edge .Operating frequencies up to 1 GHz can be expected in a standard 0.35 ~C MOS technology. In DSRC DC-Stability and signal reliability are fulfilled by FM0 and Manchester In [6] presents a review on evaluation of various forms of DSRC system. DSRC is the only short-range wireless alternative today that provides Fast Network Acquisition, Low Latency, High Reliability when Required, Priority for Safety Applications, Interoperability, Security and Privacy which is one of the challenging task faced by all in the worldwide.

In [7] proposed a fully reused VLSI architecture using the SOLS technique for both FM0 and Manchester encoding. The SOLS technique eliminates the limitation of hardware utilization by two core techniques: area compact retiming and balance logic-operation sharing. The SOLS technique improves the hardware utilization rate from 57.14% to 100% for both FM0 and Manchester encodings. In [8] proposed a fully reused VLSI architecture using SOLS technique for both FM0 and Manchester encodings. The coding diversity between FM0, Manchester and Miller encodings causes the limitation on hardware utilization of VLSI architecture design. In [9] proposed a system to minimize the problem of coding-diversity between FM0 and Manchester encodings that causes the limitation on hardware utilization of VLSI architecture design. In this paper, the fully reused VLSI architecture using SOLS technique for both FM0 and Manchester encodings is proposed. Area compact retiming and balance logic operation sharing are the two core techniques that are used to eliminate the limitation on hardware utilization by reducing the number of transistor and by combining the resources of FM0 and Manchester encodings.

# III. PROPOSED ARCHITECTURE

In the proposed method we are introducing Miller encoding to the present structure. In the above papers, they are discussed about the fully reused architecture of FMO and Manchester Encoding using SOLS Technique.

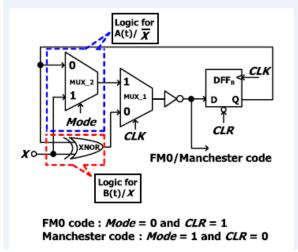

Figure 2: VLSI Architecture of FMO/ Manchester using SOLS Technique

ISSN: 2455-8761

www.ijrerd.com || Volume 02 – Issue 06 || June 2017 || PP. 111-115

The selection of FM0 or Manchester code depends on Mode and CLR signals. The CLR signal is used to reset all the contents. In addition, the CLR further has another individual function of a hardware initialization. If the CLR is simply derived by inverting Mode without assigning an individual CLR control signal, this leads to a conflict between the coding mode selection and the hardware initialization.

To avoid this conflict, both Mode and CLR are assumed to be separately allocated to this design from a system controller. Whether FM0 or Manchester code is adopted, no logic component of the proposed VLSI architecture is wasted. Every component is active in both FM0 and Manchester encodings while using the SOLS Technique. Miller encoding is also known as delay encoding. It can be used for higher operating frequency and it is similar to Manchester encoding except that the transition occurs in the middle of an interval when the bit is 1. While using the Miller delay, noise interference can be reduced. Miller encoding is combined to FMO and Manchester encoding in order to avoid the complexity of the structure.

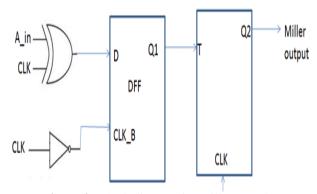

Figure 3: Block diagram for Miller encoder

The block diagram has a d flip flop, t flip flop, NOT gate, and XOR gate. Where the input is A\_in and CLK, then the output is a Miller output. For example, if the input is 0 and the clock, given the XOR operation has done that, is A\_in CLK, therefore 0 plus a positive edge clock produces the output as 0. Given to d flip flop, the clock has inverted, and after that output is given to t flip flop it inputs as d flip flop output, which is 0. Then the TFF is toggle FF, which produces the Miller output as 1.

In the proposed system, We have to effectively combines Miller encoding to the existing structure. Using SOLS Technique, we can share the same logic components between Miller and existing system. Both structures contain DFF and XOR. First divide the XNOR gate into XOR and inverter gate.

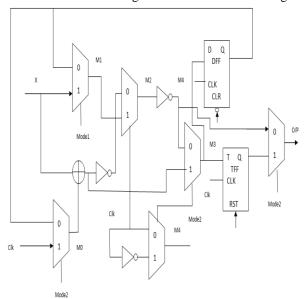

Figure 4: Fully Reused VLSI Architecture of FMO/ Manchester and Miller Encodings

In Fig. 4 Multiplexers are introduced to effectively combines both three encodings. Miller encoding needs negative clock. There are two mode signals are there one is mode1and mode2. If mode1 is active, it selects either FMO or Manchester according to the input signal X. If mode2 is active, Miller Encoding is

ISSN: 2455-8761

www.ijrerd.com || Volume 02 – Issue 06 || June 2017 || PP. 111-115

selected. CLR signal is present here to reset all the contents if Manchester encoding is selected. Without SOLS Technique, components used for the hardware architecture will be high. So power consumption of the structure, Area and delay will be high. SOLS Technique improves the Hardware Utilization Rate to 100%. The SOLS Technique classified into two techniques called Area compact retiming and Balance logic operation sharing to improve HUR and also to reduce Power, Area and Delay of the VLSI Architecture.

#### RESULTS AND DISCUSSION IV.

First modify the Hardware Architecture with Miller encoder without using SOLS Technique. SOLS technique includes Area compact retiming and Balance logic operation sharing. These two methods relocates hardware resources and sharing the same logic components between them. So the number of components will be high. It have poor Hardware Utilization Rate. Using SOLS Technique, Hardware utilization rate can be improved upto 100%. No even a single component is wasted. Then modify the fully reused structure of FMO and Manchester with Miller encoding using SOLS Technique.

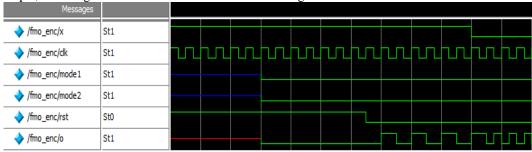

Fig. 5 shows the simulation results without using SOLS Technique. Two mode signals are used here. The number of logic components are high. So this structure consumes more power. The number of logic components are high. It leads to increase in ciruit area and also increase the delay of the circuit. While using SOLS Technique, Reset signal is removed and CLR and MODE signals are used.

Figure 5: Simulation results without SOLS Technique

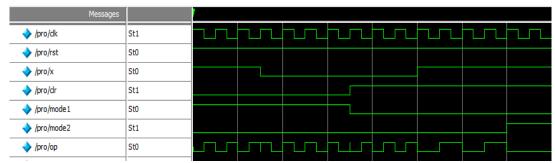

Fig.6 shows the simulation results using SOLS Technique. Three mode signals are used here. The simulation results in both cases are same.

Figure 6: Simulation results using SOLS Technique

Xilinx tools are used to calculate the Power, Area and Delay in the above both cases. From the table, we can see that the reduction of power, area and delay of our proposed system while using SOLS Technique.

**Table 1:** Comparison Table of Power, Area and Delay

|       | Without SOLS | With SOLS |

|-------|--------------|-----------|

|       | Technique    | Technique |

| Power | 672 mW       | 167mW     |

| Area  | 70           | 61        |

| Delay | 11.839       | 9.59      |

# V. CONCLUSION

In this paper, we have proposed a fully reused VLSI Architecture of FMO/ Manchester and Miller encoder using SOLS Technique for DSRC Applications. The SOLS technique eliminates the limitation on hardware utilization by two core techniques: area compact retiming and balance logic-operation sharing. The

ISSN: 2455-8761

www.ijrerd.com || Volume 02 – Issue 06 || June 2017 || PP. 111-115

area-compact retiming relocates the hardware resource to reduce the transistors. The balance logic-operation sharing efficiently combines FM0 and Manchester and Miller encodings with the identical logic components.

## **REFERENCES**

- [1] Yu-Husan Lee and Cheng-Wei Pan, "Fully Reused VLSI Architecture of FM0 and Manchester Encoding using SOLS Technique for DSRC Applications", IEEE Transaction on Very Large Scale Integration system Vol.23, NO.1, pp.19-29 January 2015.

- [2] S.P Ramekar and Dr.P.N. Chatur, "A Review on Fully Utilized Architecture for FM0, Manchester and Miller Encoding Using SOLS Technique", International Journal of Innovative Research in Computer and Communication Engineering, Vol. 4, Issue 2, pp.2517-2523 February 2016.S. Zhang, C. Zhu, J. K. O. Sin, and P. K. T. Mok, "A novel ultrathin elevated channel low-temperature poly-Si TFT," IEEE Electron Device Lett., vol. 20, pp. 569–571, Nov. 1999.

- [3] Lalitha V, and Kathiravan s, "A Review of Manchester, Miller, and FM0 Encoding Techniques", Smart Computing Review, vol. 4, no. 6, pp.481-490 December 2014.

- [4] P. Benabes, A.Gauthier, and J.Oksman, "A Manchester code generator running at 1 GHz," in *Proc. IEEE, Int. Conf. Electron., Circuits Syst.*, vol. 3. Dec. 2003, pp. 1156–1159. vol. 3. Dec. 2003, pp. 1156–1159.

- [5] Supriya S. Garade, and P. R. Badadapure, "Review of Fully Reused VLSI Architecture of Channel Encoding Using SOLS Technique for DSRC Applications", International Journal of Science and Research (IJSR), Volume 5 Issue 4, pp.2313-2315April 2016.

- [6] M. Abinaya, and T. Suganya Thevi, "Evaluation of Various Forms of DSRC System- A Review", International Journal of Engineering Science Research Technology, November, 2014.

- [7] T Sravan Kumar, and A. Madhukar Babu, "FM0/Manchester Encoding for DSRC Applications Using SOLS Technique", Journal Research in Electrical Electronics and communication, Vol.3, Issue 6.

- [8] Ms. Jomcy Rani Xavier, and Dr. U. A.Kshirsagar, "Fully Reconfigured VLSI architecture of FM0, Manchester and Miller", International Journal of Engineering Research and General Science Volume 4, Issue 2,pp.839-846 March- April, 2016.

- [9] T.Rajini, and G.Sataya Prabha, "Fully Rrused VLSI Architecture Of FM0/Manchester Encoding Using SOLS Technique For DSRC Application", International Journal of Research In Advance Engineering Technologies, Volume 5, Issue 1, pp.33-40, SEP 2015.